|

커패시터 멀티플라이어를 갖는 CCM/DCM 이중모드 DC-DC 벅 컨버터의 설계 |

|

최진웅1, 송한정1,2* 1인제대학교 나노융합공학과, 2인제대학교 나노매뉴팩처링 연구소

|

|

Design of a CCM/DCM dual mode DC-DC Buck Converter with Capacitor Multiplier |

|

Jin-Woong Choi1, Han-Jung Song1,2* 1Department of Nanoscience & Engineering, Inje University 2Center for nano Manufactoring, Inje University |

|

요 약 본 논문에서는 휴대 전자기기의 내부 전원단을 위한, CCM/DCM 기능의 이중모드 감압형 DC-DC 벅 컨버터를 제안한다. 제안하는 변환기는 1 MHz의 주파수에서 동작하며, 파워단과 제어블럭으로 이루어진다. 파워단은 Power MOS 트랜지스터, 인덕터, 커패시터, 제어 루프용 피드백 저항으로 구성된다. 제어부는 펄스폭 변조기 (PWM), 오차증폭기, 램프 파 발생기, 오실레이터 등으로 이루진다. 또한 본 논문에서 보상단의 큰 외부 커패시터는, 집적회로의 면적축소를 위하여 CMOS 회로로 구성되는 멀티플라이어 등가 커패시터로 대체하였다. 또한,. 본 논문에서, 보상단의 외부 커패시터는 집적회로의 면적을 줄이기 위하여 곱셈기 기반 CMOS 등가회로로 대체하였다. 또한 제안하는 회로는 칩을 보호하기 위하여 출력 과전압, 입력부족 차단 보호회로 및 과열 차단 보호회로를 내장하였다. 제안하는 회로는 0.18 ㎛ CMOS 공정을 사용하여, 케이던스의 스펙트라 회로설계 프로그램을 이용하여 설계 및 검증을 하였다. SPICE 모의 실험 결과, 설계된 이중모드 DC-DC 벅 변환기는 94.8 %의 피크효율, 3.29 mV의 리플전압, 2.7 ~ 3.3 V의 전압 조건에서 1.8 V의 출력전압을 보였다.

|

|

Abstract This paper presents a step-down DC-DC buck converter with a CCM/DCM dual-mode function for the internal power stage of portable electronic device. The proposed converter that is operated with a high frequency of 1 ㎒ consists of a power stage and a control block. The power stage has a power MOS transistor, inductor, capacitor, and feedback resistors for the control loop. The control part has a pulse width modulation (PWM) block, error amplifier, ramp generator, and oscillator. In this paper, an external capacitor for compensation has been replaced with a multiplier equivalent CMOS circuit for area reduction of integrated circuits. In addition, the circuit includes protection block, such as over voltage protection (OVP), under voltage lock out (UVLO), and thermal shutdown (TSD) block. The proposed circuit was designed and verified using a 0.18 ㎛ CMOS process parameter by Cadence Spectra circuit design program. The SPICE simulation results showed a peak efficiency of 94.8 %, a ripple voltage of 3.29 mV ripple, and a 1.8 V output voltage with supply voltages ranging from 2.7 to 3.3 V.

Keywords : Buck, CCM, CMOS, DC-DC converter, DCM, Integrated circuit, SPICE |

1. 서론

전력 반도체 기술 분야 중에서 최근 각광을 받고 있는 휴대기기용 PMIC는 휴대기기에 전원 공급 및 관리하는 장치로 수요가 점점 증가하고 있다 [1-2]. 이러한 휴대기기들은 배터리 전원으로부터 다양한 내부 시스템에 전원을 공급하여야 한다. 그러므로 배터리 전압을 내부 시스템 전원 전압으로 전력 변환 하는 IC는 장시간 사용하기 위해 넓은 부하조건에서 높은 효율을 갖는 DC-DC 컨버터가 필요하다 [1]. 따라서 이를 구현하기 위한 다양한 PMIC 개발이 증가하고 있다. 기존에 많이 사용되는 PWM 제어 방식은 중부하(Medium load)서 효율이 높으나 경부하 (Light load)에서는 스위칭 손실 증가로 인해 효율이 매우 감소한다 [3]. 특히 휴대기기의 Standby 상태에서는 큰 문제로 대두되고 있다.

본 논문에서 제안된 집적회로는 0.18 ㎛ 공정을 이용하여 설계하였으며, 보상단의 큰 커패시터를 집적화 하기 위해 커패시터 멀티플라이어 기법을 사용하여 칩을 설계하였다 [4].

2. DC-DC 벅 컨버터

2.1 DC-DC Buck Converter의 구성 및 원리

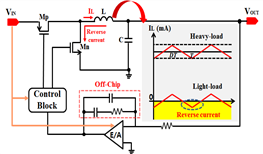

그림 1은 기존의 DC-DC 벅 컨버터의 블록도를 나타낸 것이다. 기존의 감압형 DC-DC 컨버터의 구조는 Power MOSFET과 스위치의 on/off를 담당하게 될 컨트롤 블록으로 구성된다. DC-DC 벅 컨버터는 로드저항에 따라 효율이 달라진다. 일반적으로 로드저항이 커져서 벅 컨버터의 출력전류가 줄어들면 (Light load), 이 때 그림 1에서 보이는 것과 같이 역 전류가 흐르게 되어 효율이 감소하게 된다. 따라서 이러한 역 전류를 흐르지 않게 하기 위한 제어기가 필요하다. 뿐만 아니라 집적화를 위해 보상단의 큰 커패시터를 커패시터 멀티플라이어로의 대체도 요구된다 [4].

Fig. 1. Block diagram od the conventional DC-DC buck converter

2.2 이중모드 DC-DC Buck Converter

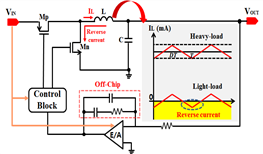

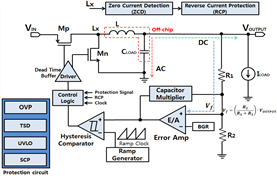

그림 2에 제안하는 이중모드 DC-DC Buck Converter의 블록도를 나타내었다. 제안하는 회로는 Power MOS (NMOS, PMOS), 인덕터, 커패시터, 저항으로 구성되는 파워 부분과 PWM신호를 생성하는 컨트롤러 부분으로 이루어진다. 또한 칩을 보호하기 위한 UVLO (Under Voltage Lock Out; 저전압 보호 회로), OVP (Over Voltage Protection; 고전압 보호회로), TSD (Thermal Shut Down; 과열 보호회로) 등 보호회로를 내장하였다.

Fig. 2. Proposed dual mode buck converter

부하가 중부하 (50 mA ~ 350 mA)로 동작 시 CCM (Continuous Conduction Mode)로 동작하여 안정적인 PWM 파형을 출력하며, 부하가 경부하 (10 mA ~ 50 mA)로 동작 시 ZCD (Zero Current Detection)회로에서 영전류를 검출하여 RCP (Reverse Current Protection)회로를 거쳐 DCM (Discontinuous Conduction Mode)로 동작하여 역전류를 차단하고 효율을 보상하게 된다 . 이러한 동작 알고리즘을 그림 3에 나타내었다.

Fig. 3. Operation algorithm in CCM/DCM mode

|

Parameter |

Spec. |

Units |

|

Supply Voltage |

3.7 |

V |

|

Output Voltage |

1.8 |

V |

|

Switching Frequency |

1 |

MHz |

|

efficiency |

90 |

% |

|

Load Current |

350 |

mA |

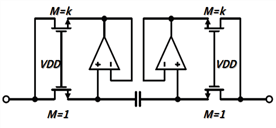

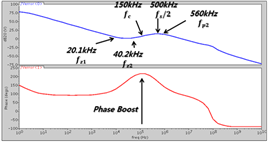

2.3 멀티플라이어 커패시터

DC-DC 컨버터의 피드백 시스템에서 안정화를 위해 보상단의 역할이 중요하다 [5]. 보상단은 큰 커패시터와 저항으로 구성되는데, 칩의 부피가 상당히 커진다. 이러한 단점을 보완하기 위해 큰 커패시터 대신에 CMOS 회로로 커패시터 특성을 갖도록 설계하여 구현하였다. 보상단의 멀티플라이어 커패시터 회로를 그림 4(a)에 나타내었다. 이러한 부피가 줄어든 커패시터 멀티플라이어 회로를 사용하여 DC-DC 벅 변환기의 위상마진, 발진 등의 안정성에 대한 요건들을 조절하였다.

(a)

(b)

Fig. 4. Equivalent capacitor using multipliers

(a) schematic (b) AC analysis

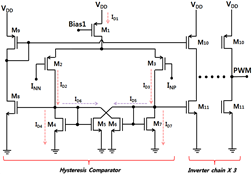

2.4 히스테리시스 비교기 및 오차증폭기

그림 5의 히스테리시스 비교기 (Hysteresis comparator)는 PWM제어 신호를 출력하기 위해 Error Amp의 출력과 삼각파를 입력으로 받아 스위칭 펄스를 출력한다. 이 비교기는 높은 이득을 가지는 정궤환의 소스 결합 차동쌍 (Source-Coupled differential pair)으로 구성되어 있다.

Fig. 5. Hysteresis comparator

인버터 체인 (Inverter Chain)단은 비교기의 출력 응답 속도를 상승시키기 위해 사용되었다.

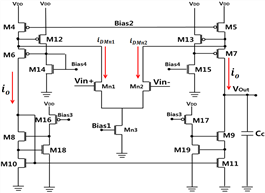

오차증폭기는 DC-DC Buck Converter의 출력 전압을 피드백 (Feedback) 받아 기준 전압과 비교 후 입력 간의 차이를 증폭하여 출력한다 [6]. 본 논문에서 사용한 에러앰프 (Error Amplifier)의 회로도 및 동작원리는 그림 6에 나타내었다. 기존의 폴디드캐스코드 앰프 (Folded Cascode Amplifier)에서 공통 소스단 (Common Source)을 삽입하여 출력 저항을 증가시킴으로써 높은 전압이득을 얻을 수 있다. 에러앰프의 높은 전압이득은 피드백 에러율 (Feedback Error Ratio)을 감소시킬 뿐만 아니라 Transient Response 특성을 향상시킨다.

Fig. 6. Schematic of the error amplifier

에러앰프의 동작 원리로는 M11의 드레인 전압이 감소 시 M19가 차단되어 M9의 VGS가 상승하여 ![]() 가 증가한다. 또한

가 증가한다. 또한 ![]() 가

가 ![]() 보다 15 % 더 큰 값을 가지게 함으로써 출력 단의 왜곡이 생기지 않도록 하였다. 이는 안정적인 Current Reference를 가지므로 이후 보상 문제에서 안정적인 전류 레벨을 가질 수 있다.

보다 15 % 더 큰 값을 가지게 함으로써 출력 단의 왜곡이 생기지 않도록 하였다. 이는 안정적인 Current Reference를 가지므로 이후 보상 문제에서 안정적인 전류 레벨을 가질 수 있다.

3. DC-DC 벅 컨버터 모의실험 결과

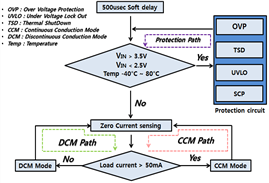

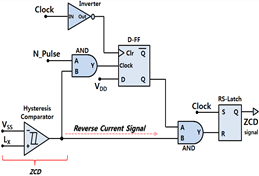

스위칭 컨버터를 설계 시 고려해야 할 사항으로 스위칭 주파수 및 인덕턴스 등을 고려하여 인덕터에 흐르는 충.방전 전류를 설정한다. Low side 스위치 대신 환류 다이오드를 사용 할 시 경부하에서 DCM에서 동작하게 되어 인덕터의 흐르는 전류가 0 이하의 값이 되면 전류가 흐르지 않는다. 하지만 고주파의 스위칭 주파수에서는 다이오드의 리커버리 (Recovery)특성이 떨어져서 추가적인 손실이 발생하므로 싱크로너스(Synchronous) 타입의 스위치 방식으로 설계한다. 싱크로너스 타입의 경우 DCM으로 자동 전환되지 않아 경부하시 역전류로 인한 손실이 발생하므로 인덕터 전류가 0 mA시 전류를 차단하여야 한다. 본 논문에서는 역전류 발생 시 ZCD회로에서 영전류를 검출 후 RCP 회로를 거쳐 DCM모 드로 전환됨으로써 경부하시 효율을 보상하는 방법을 제시한다. ZCD 및 RCP 회로는 그림 7에 나타내었다.

Fig. 7. Schematic of the ZCD (zero current detector)

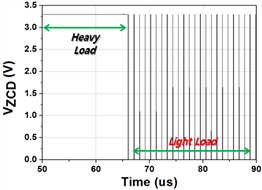

역전류가 발생하면 Low side 스위치에서 전류가 Lx노드에서 GND (Ground)로 흐르게 되어 노드 Lx의 전압이 GND보다 높아지게 된다. 영전류가 감지되면 비교기에서 High 값을 출력하게 되며, Clock 신호에 의해 주기적으로 Reset이 되며 D-FF 및 RS-Latch등의 로직 (Logic)을 통해 역전류의 신호를 얻을 수 있다. 그림 8에서 경부하 조건시의 영전류 검출 신호 파형을 나타내었다.

Fig. 8. Zero current detected signal in condition heavy and light load

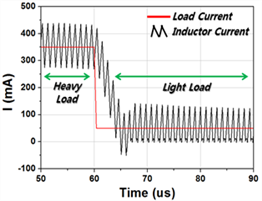

영전류 신호를 DC-DC Buck Converter의 Control Logic을 통해 CCM/DCM 모드가 전환되며 이를 그림 9에 나타내었다.

Fig. 9. CCM/DCM mode transfer simulation

중부하시 인덕터 전류는 CCM에서 동작하나 경부하시 0 mA 이하를 지나는 역전류는 차단되어 DCM모드로 동작하는 결과를 보였다.

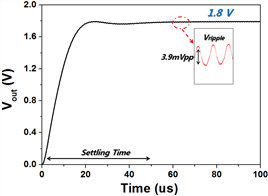

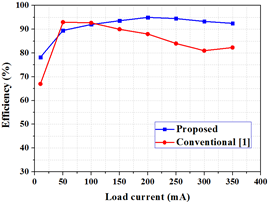

그림 10에 제안하는 DC-DC buck Converter의 출력 전압을 나타내고 있다. 출력전압은 1.8 V, 리플 (Ripple)은 약 4 mV가 출력 되는 것을 확인 할 수 있었다. 그림 11은 로드전류에 따른 효율 특성을 나타 낸 것이다. 경부하시에 낮은 효율을 보상하여 기존의 DC-DC Buck Converter [1]의 경부하 조건보다 10 %의 효율 상승을 보였다. 표 2에 본 논문에서 제안하는 변환기와, 최근 발표된 유사한 기능을 갖는 전류모드 방식의 DC-DC 벅 변환기[1]와 성능비교를 하였다.

Fig. 10. Simulated output of the dual mode DC-DC buck converter

Fig. 11. Efficiency of the dual mode DC-DC buck converter

|

Subject |

[1] |

This work |

|

IC process |

0.35 µm |

0.18 µm |

|

Input voltage |

2.5~3.3V |

2.7~3.3V |

|

Output Voltage |

0.9-3.1V |

1.8V |

|

Clock |

1MHz |

1MHz |

|

Max. output current |

750mA |

500mA |

|

Compensator(capacitor) |

N/A |

on-chip |

|

Peak efficiency |

93.5% |

94.8% |

|

Ripple |

15mV |

3.29mV |

4. 결론

본 논문에서는 이중모드 DC-DC Buck Converter를 설계하여 0.18 μm 공정을 이용하여 시뮬레이션을 통해 회로를 분석하였다.. 설계된 이중모드 DC-DC Buck Converter는 2.7 V ~ 3.3V 의 입력 전압에 대해서 출력 전압이 1.8 V로 나왔고, 출력전류는 0 mA ~ 350 m A로, 넓은 부하조건에서도 구동이 가능할 것으로 보인다. 또한, 경부하시에 낮은 효율을 보상하여 기존의 DC-DC buck converter의 경부하 조건보다 10 %의 효율 상승을 보였다. 뿐만 아니라 커패시터 멀티플라이어 기법을 사용하여 벅 컨버터의 면적을 줄일 수 있었다. 제안하는 이중모드 DC-DC buck converter는 넓은 부하 범위를 가지는 휴대기기에 매우 적합한 기술로 사용이 될 것이다.

References

[1] Youngkook Ahn and Jeongjin Roh, "A 93.5% Efficiency, 400mA Cufrrent-Mode DC-DC Buck Converter with Watchdog functions", ISOCC 2009

[2] L. M. Piao, "A study on Design of PMIC of SEPIC/BOOST Topology with Integrated current sensing circuit", Inha University Master degree , 2011.

[3] X. Zhang, P. Chen, Y. Okuma, K. Ishida,Y. Ryu, K. Wa anabe, T. Sakurai and M. Takamiya, “A 0.6-V Input 94% Peak Efficiency CCM/DCM Digital Buck Converter in 40-nm CMOS with Dual-Mode-Body- Biased Zero-Crossing Detector”, IEEE Asian Solid-State Circuits Conf, 2013.

DOI: http://dx.doi.org/10.1109/ASSCC.2013.6690978

[4] Ying Jianhua and Huang Yang, "Design of an LDO with capacitor multiplier." Journal of Semiconductors, vol. 31, no. 7, pp. 075010-1-075010-4, 2010.

DOI: http://dx.doi.org/10.1088/1674-4926/31/7/075010

[5] K.N. Leung and P.K.T.Mok, "Analysis of multi-stage amplifier Frequency compensation", IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 48, no. 9, pp. 1041-1056, 2001.

DOI: http://dx.doi.org/10.1109/81.948432

[6] Jeonsin Roh, "High-performance Error Amplifier For Fast Transient DC-DC Converters". IEEE Tran. Circuits and Systems, vol. 40, no. 11, pp. 591-595, 2005.

DOI: http://dx.doi.org/10.1109/TCSII.2005.850521

|

최 진 웅(Jin-Woong Choi) [준회원] |

|

|

|

•2015년 2월 : 인제대학교 나노융합공학부 (공학사) •2015년 2월 ~ 현재 : 인제대학교 나노융합공학과 재학중 |

|

<관심분야> 반도체, 회로설계, 소자 |

|

|

송 한 정(Han-Jung Song) [정회원] |

|

|

|

•1986년 2월 : 한양대학교 전자공학과 (공학사) •1988년 2월 : 한양대학교 전자공학과 (공학석사) •2000년 2월 : 한양대학교 전자공학과 (공학박사) •2004년 3월 ~ 현재 : 인제대학교 나노공학부 정교수 |

|

<관심분야> 반도체 소자 신뢰성 및 회로설계 |

|