# DCM PFC 플라이백 컨버터의 스위칭 피크 전류 저감을 위한 Switching Duty Cycle Split 방식

박대수, 김태경, 오성철<sup>\*</sup> 한국기술교육대학교 전기전자통신공학부

# A Switching Duty Cycle Split Method of DCM PFC Flyback Converter for Reducing Switch Peak Current

Dae-Su Park, Tae-Kyung Kim, Sung-Chul Oh\*

School of Electrical, Electronics and Communication Engineering,

Korea University of Technology and Education

요 약 에너지 효율이 낮은 백열등이나 형광등에서 에너지 효율이 높은 LED로 대체하면서 관련 규격에서는 LED 드라이 버에 대하여 역률과 왜곡률에 대한 요구를 하고 있다. 이에 따라 본 논문에서의 주회로 출력측 리플 저감을 위해 1차측에 Coupled Inductor와 출력 커패시터 용량을 줄이기 위해 2차측에 LC 공진을 적용한 Coupled LC 공진 Flyback 컨버터를 사용하였으며, 역률보상(PFC, Power Factor Correction)으로 불연속전도모드(DCM, Discontinuous Conduction Mode)이 널리 사용되고 있지만, 경계전도모드(BCM, Boundary Conduction Mode)보다 스위치에 흐르는 전류의 피크값이 높아 소자들의 스트레스가 증가하는 단점이 있다. 이를 보완하기 위해서 1차측과 2차측의 피크 전류를 저감하기 위하여 듀티비 분할 방식을 제안하였다. 제안한 방식의 검증을 위해 PSIM을 이용한 시뮬레이션을 통하여 기존 제어 방식(무분할 방식)과 제안한 듀티비 분할 방식을 지연시간 및 분할 수에 따른 스위치에 흐르는 전류 피크값을 비교하였다. 시뮬레이션 결과를 비교해보면 듀티비 분할 방식이 기존 방식에 비해 전류 피크값과 출력 리플이 1차측 전류 16%, 2차측 전류 22%, 출력 리플 4%로 저감 하는 것을 확인 하였다.

Abstract The IEC standard stipulates the requirements for power factor and distortion factor in LED drivers when substituting low energy-efficiency incandescent or fluorescent lamps with high energy-efficiency LED lamps. To meet such regulations, this study used a Coupled LC Resonance Flyback converter, which adopted a coupled inductor at the primary side to reduce the ripple at the output of the main circuit and LC resonance at the secondary side to reduce the capacity of the output capacitor. On the other hand, when DCM (discontinuous conduction mode) was operated for PFC (power factor correction), the stresses on devices are increased due to the greater magnitude of the peak current on switch than the one in BCM (boundary condition mode). To overcome such issues, this paper proposes a duty cycle split method to reduce the maximum peak current at the primary and secondary sides of the converter. Moreover, to validate the proposed method, this paper compares the magnitude of peak currents on switch between applying the proposed duty cycle split method and the existing control method (non-split method) according to the delay time and number of splits through simulations using PSIM. The simulation result confirmed that the duty cycle split method could reduce 16% of the peak current at the primary side, 22% of the peak current at the secondary side, and 4% of the output ripple.

Keywords: PFC, Flyback Converter, DCM, Switching Split, Switch Current Reduction

"이 논문은 2020년도 한국기술교육대학교 교수 교육연구진흥과제 지원에 의하여 연구되었음"

\*Corresponding Author: Sung-Chul Oh(Korea University of Technology and Education)

email: scoh@koreatech.ac.kr

Received March 22, 2022 Accepted June 3, 2022 Revised May 24, 2022 Published June 30, 2022

# 1. 서론

최근에, 전원 공급 장치에 있어서 파워의 품질에 대한 요구가 높아지고 있다. IEC 61000-3-2 규격은 조명을 위한 AC/DC 전원 공급 장치에 대하여 역률(PF)과 전체 파형 왜곡률(THD)에 대한 규격을 만족하도록 요구하고 있다[1].

LED driver의 구조는 크게 1단 구조와 2단 구조로 나 뉜다. 1단 구조에서는 교류 입력을 직류 출력으로 적합 하게 바꾸는 역률 보상 회로와 직류 입력을 원하는 직류 출력으로 바꾸는 컨버터가 하나의 스위치를 같이 사용하 여 하나로 합쳐지게 된 구조이다.

2단 구조 컨버터에서는 1단 구조에 비해 입력 전압이 나 출력 전력이 바뀌어도 연결 커패시터 전압이 일정하 다. 이는 역률 보상 회로와 DC-DC 변환 컨버터 부분이 분리되어 각각의 컨트롤러에 의해 따로 동작하기 때문이 다[2].

따라서, 부품의 수가 적고, 변압기의 권선비를 통해 출력 전압을 쉽게 가변시킬 수 있으며 절연이 가능한 1 단 구조의 Flyback 컨버터를 사용한다.

본 논문에서는 기존의 Coupled LC 공진 Flyback 컨 버터에 역률 보상을 위해 역률보상의 불연속전도모드를 사용하였으며, 불연속전도모드의 경우 입력 전류를 불연속 전류 모드로 제어하는 방식으로서 입력 전류나 전압을 검출할 필요 없이 고정 주파수에 의해 일정한 시비율로 스위칭하여 스위치 전류의 피크 값이 입력 전압을 추정하게 된다[3]. 그래서 본 논문에서는 리플 저감을 위한스위치 전류의 피크 값을 줄이기 위해 스위치의 듀티비분할 방식을 제안하였다.

그리고 듀티비 분할 방식을 주회로에 적용하였으며, PSIM을 이용하여 듀티비 분할의 수와 지연시간에 따른 입력 전류의 피크값을 비교하였다.

# 2. 1단 구조 PFC Flyback 컨버터

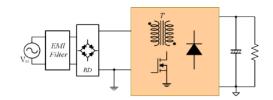

1단 구조 AC-DC 컨버터의 경우 출력에 큰 리플 성분이 존재함에도 불구하고, 가격적인 측면과 에너지 밀도에 있어서 2단 구조 컨버터와 비교해 볼 때 더 좋은 해결책이 될 수 있다. 1단 구조 AC-DC 컨버터는 교류를 직류로 직접 바꾸는 컨버터를 의미하며, 개략적인 도면을 Fig. 1에 나타내었다[4].

Fig. 1. One-stage AC-DC Coverter[4]

# 2.1 역률 보상 제어

역률을 보상하는 기법은 인덕터에 흐르는 전류의 연속-불연속을 기준으로 분류할 수 있고, 플라이 백 컨버터는 인덕터가 2권선 또는 다중 권선이며 권선비가 다르기 때문에 자화전류, 즉 자속을 기준으로 연속-불연속을 판단하며, 연속전도모드(CCM, Continuous Conduction Mode), 불연속전도모드(DCM, Discontinuous Conduction Mode), 경계전도모드(BCM, Boundary Conduction Mode)로 분류할 수 있다[5].

#### 2.1.1 연속 전도 모드

Fig. 2. Continuous Conduction Mode[3]

Fig. 2는 연속 전도 모드 방식의 파형이다. 연속전도 모드에서의 주 스위칭 시비율은 시간에 따라 변하게 된다. 출력전압에 저주파 리플이 존재하고 응답 특성이 느리지만 추종특성이 우수하다. 그러나 입력 전류 및 전압을 검출하여 입력 전류가 입력 전압을 추종하는 제어 루프를 두어야 하며 출력 전압 레귤레이션을 위한 전압 제어루프를 두어야 하는 등 제어 구조가 다소 복잡하다. 또한 출력 다이오드의 역 회복에 의한 서지 전류 등의 단점이 있다. 다른 두 방식에 비해 전류 실효치 및 첨두치가 작아 효율 및 발열이 우수하여 대용량 급(600W 이상)에 적합하다[3].

#### 2.1.2 불연속 전도 모드

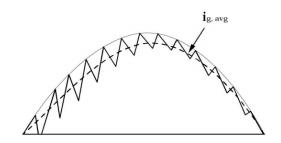

Fig. 3. DisContinuous Conduction Mode[3]

Fig. 3은 고정 주파수에서 동작하는 불연속 전도 모드 방식의 파형이다. 불연속전도모드의 경우 입력 전류를 불연속 전류 모드로 제어하는 방식으로서 입력 전류나 전압을 검출할 필요 없이 고정 주파수에 의해 일정한 시비율로 스위칭하여 스위치 전류의 피크 값이 입력 전압을 추종하게 된다. 스위치 전류의 평균값이 그대로 정현파가 되기 때문에 간단히 제어되며 경계 전도 모드와 마찬가지로 출력 다이오드 역 회복에 의한 문제는 없으나전류 파형에 왜곡이 생겨서 완전한 정현파가 되지 못하는 단점을 갖는다. 또한 연속전도모드와 경계전도모드방식에 비해 인덕터 전류의 크기가 커 100W급 이하의소용량에 주로 적용되고 있다[3].

#### 2.1.3 경계 전도 모드

Fig. 4. Boundary Conduction Mode[3]

Fig. 4는 가변 주파수에서 동작하는 경계 전도 모드 방식의 파형이다. 입력전류는 연속과 불연속의 경계에서 동작하며 고정주파수 제어와 달리 전류가 0이 되었는지 를 판단하는 영전류 검출회로(ZCD)가 추가 되어 있다. 인덕터 전류를 불연속 모드에서 동작하기 때문에 전류를 평균시키기 위한 필터의 크기가 커지게 되지만 영전류 스위칭을 하기 때문에 스위칭 손실을 줄일 수가 있다. 뿐 만 아니라 범용 제어기의 가격이 매우 저렴하므로 제작 단가 측면에서도 유리하다. 그러나 인덕터 전류가 연속 전도모드에 비해 다소 커 300W정도의 중용량 급에 주로 사용되고 있다[3].

# 2.2 PFC 스위칭 제어 방식

센싱부에서 기준전압(Vref)과 출력전압(Vsa)의 값을 비교하여 비교 값에 따른 오차만큼 보상회로(PI controller)를 통해 보상해주었으며, 전류 제어를 위해 전압의 보상값을 입력전류(Isa)를 센싱한 값과 비교 후보상회로(PI controller)를 통해 제어량을 주었고, 제어량에 맞춰 비교기를 통해 스위칭 신호를 주었다. 이에 따른 Flyback 컨버터의 제어 블록 다이어그램 구성은 Fig. 5와 같다.

Fig. 5. Conventional PFC Control Block Diagram

# 3. 게이트 분할에 따른 특성 비교

게이트 분할 방식 특성 비교를 위해서 출력 전압 보상 이 없이 분할 수 및 지연 시간에 따른 특성 분석을 위하 여 시뮬레이션을 수행하였다.

# 3.1 주회로 및 PFC 방식 선정

주회로 Coupled LC 공진 회로는 Flyback 컨버터의 출력 리플 저감을 위해 1차측에 Coupled Inductor, 다이오드와 커패시터를 사용하였으며, 2차측에는 LC 공진 필터를 적용한 회로이다.

또, 역률 보상을 위해 비교적으로 제어기가 단순한 불 연속전도모드 방식을 사용하였으나 경계전도모드 방식보 다 전류 리플이 커서 소자에 걸리는 전류 스트레스가 큰 단점을 가지고 있다.

따라서, 본 논문은 이 단점을 보완하고자 듀티비 분할 방식을 제안하였고 게이트 신호의 지연 시간에 따른 특 성 시험을 통해 불연속전도모드의 동작 시간을 보장하는 지연 시간으로 선정 하였다.

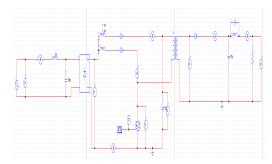

Fig. 6. Main Circuit Coupled LC Resonant Flyback Converter

3장에서는 Fig. 6은 Coupled LC 공진 회로로써 리플 저감을 위해 1차측에 Coupled Inductor와 출력 커패시터 용량을 줄이기 위해 2차측에 LC 공진을 적용한전압 보상없는 open loop인 주회로만을 가지고 무분할, 2분할, 3분할 듀티비 분할 제어 방식의 따른 타당성을 실험적으로 입증하기 위하여 주회로를 설계하였으며, Table 1은 주회로의 파라미터를 나타낸다.

Table 1. System parameters

| Parameter            | Value   |  |

|----------------------|---------|--|

| Ouput power          | 33[W]   |  |

| Oupout Current       | 1[A]    |  |

| Oupout Voltage       | 33[V]   |  |

| Switching Frequentcy | 40[kHz] |  |

| Duty Ratio           | 0.15    |  |

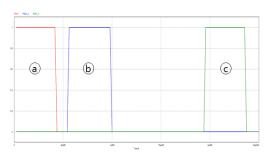

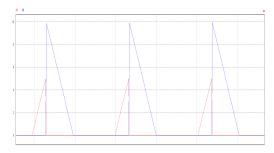

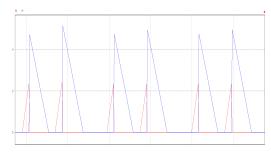

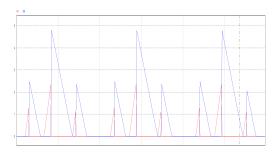

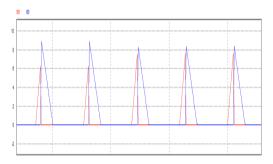

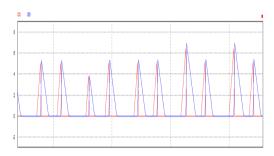

Fig. 7과 Fig. 8은 한 주기의 게이트 신호를 지연시간 과 분할에 따라 나타낸 파형이다. Fig. 7은 위상 변환에 따른 주회로의 스위칭 듀티비이며, Fig. 7과 같이 각각 a(0), b(5.55u), c(19.44u)으로 지연 시간을 주었다.

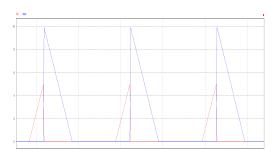

Fig. 7. Switching Duty Cycle

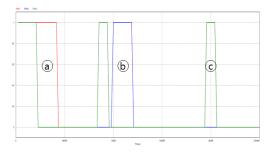

Fig. 8은 주회로의 무분할과 2분할 그리고 3분할에 따른 스위치 듀티비이며, Fig. 8과 같이 각각 무분할은 a(0), 2분할은 b(0과 9.79u), 3분할은 c(0과 8.33u, 19.44u)으로 분할하여 지연 시간을 주었다.

Fig. 8. Switching Duty Cycle Split

# 3.2 듀티비 무분할(지연 시간 : 0)

Fig. 9. Switching current and diode current waveform of duty cycle non-split (Delay time: 0)

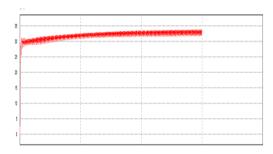

Fig. 10. Output voltage waveform of duty cycle non-split (Delay tiem: 0)

Fig. 9는 듀티비 무분할(지연 시간: 0) 스위치 전류와 2차측 다이오드 전류 파형으로 4.92A, 9.99A로 측정 되었다. Fig. 10은 회로의 출력 전압으로 34.93V로 0.35V의 리플이 측정 되었다.

# 3.3 듀티비 무분할(지연 시간 : 5.55u)

Fig. 11. Switching current and diode current waveform of duty cycle non-split (Delay tiem: 5.55u)

Fig. 12. Output voltage waveform of duty cycle non-split (Delay tiem: 5.55u)

Fig. 11은 듀티비 무분할(지연 시간: 5.55u) 스위치 전류와 2차측 다이오드 전류 파형으로 4.95A, 9.96A로 측정 되었다. Fig. 12은 회로의 출력 전압으로 34.96V로 0.35V의 리플이 측정 되었다.

# 3.4 듀티비 무분할(지연 시간: 19.44u)

Fig. 13. Switching current and diode current waveform of duty cycle non-split (Delay tiem: 19.44u)

Fig. 14. Output voltage waveform of duty cycle non-split (Delay tiem: 19.44u)

Fig. 13은 듀티비 무분할(지연 시간: 19.44u) 스위치 전류와 2차측 다이오드 전류 파형으로 각각 5.06A, 9.84A로 측정 되었다. Fig. 14는 회로의 출력 전압으로 34.97V로 0.35V의 리플이 측정 되었다.

# 3.5 듀티비 2분할(지연 시간: 0, 9.79u)

Fig. 15. Switching current and diode current waveform of duty cycle two split (Delay time: 0, 9.79u)

Fig. 16. Output voltage waveform of duty cycle two split (Delay time: 0, 9.79u)

Fig. 15은 듀티비 2분할(지연 시간: 0, 9.79u) 스위치 전류와 2차측 다이오드 전류 파형으로 스위치 전류는 2.26A, 2.49A로 2차측 다이오드 전류는 4.78A, 4.81A로 측정 되었다. Fig. 16는 회로의 출력 전압으로 26.25V로 0.13V의 리플이 측정 되었다.

# 3.6 듀티비 3분할(지연 시간 : 0, 8.33u, 19.44u)

Fig. 17. Switching current and diode current waveform of duty cycle three split (Delay time: 0, 8.33u, 19.44u)

Fig. 18. Output voltage waveform of duty cycle three split (Delay time: 0, 8.33u, 19.44u)

Fig. 17은 듀티비 3분할(지연 시간 : 0, 8.33u, 19.44u) 스위치 전류와 2차측 다이오드 전류 파형으로 1차 전류는 1.26A, 2.34A, 1.1A로 2차 전류는 2.46A, 4,78A, 2.35A로 측정 되었다. Fig. 18은 회로의 출력 전압으로 23.07V로 0.11V의 리플이 측정 되었다.

# 3.7 듀티비에 따른 특성 비교

Table 2에 듀티 분할 및 지연시간에 따른 스위치 전류, 다이오드전류, 출력전압, 리플을 각각 비교한 결과 듀티비 분할의 수와 지연시간에 따라 차이가 있는 것을 확인할 수가 있다. 분할의 수를 늘릴수록 스위치 전류와 2차측 다이오드 전류는 저감하였으나 출력 전압도 같이 저감하는 것을 확인 할 수 있었다. 따라서, 본 논문은 스위치 전류와 2차측 다이오드 전류의 피크값을 저감하기위해 스위칭의 시비율을 2분할 방식을 선정 하였으며, 출력 전압이 저감되는 단점을 보완하기 위해 스위칭 제어를 통하여 출력 전압을 보상하는 방식을 제안 하였다.

Table 2. Simulation results and circuit comparison table

| Duty split and delay time                           | switching<br>current     | diode<br>current          | output<br>voltage | ripple |

|-----------------------------------------------------|--------------------------|---------------------------|-------------------|--------|

| Duty non-split<br>(delay time : 0)                  | 4.92A                    | 9.99A                     | 34.93V            | 0.35V  |

| Duty non-split<br>(delay time : 5.55u)              | 4.95A                    | 9.96A                     | 34.96V            | 0.35V  |

| Duty non-split<br>(delay time: 19.44u)              | 5.06A                    | 9.84A                     | 34.97V            | 0.35V  |

| Duty 2 split<br>(delay time : 0, 9.79u)             | 2.26A,<br>2.49A          | 4.78A,<br>4.81A           | 26.25V            | 0.13V  |

| Duty 3 split<br>(delay time : 0, 8.33u,<br>19.44u). | 1.26A,<br>2.34A,<br>1.1A | 2.46A,<br>4.78A,<br>2.35A | 23.07V            | 0.11V  |

#### 4. 제안하는 방식

본 논문에서는 역률보상 불연속전도모드의 단점인 전류 스트레스를 저감하기 위해서 주회로의 듀티비를 분할 방식을 통한 스위치 및 2차측 다이오드 전류의 피크값을 저감 하였다. 듀티비 분할은 시뮬레이션을 통해 2분할하는 방식을 제안하였으며, 출력 전압이 줄어드는 단점을 보완하고자 제어로직을 사용하였다.

#### 4.1 제안하는 스위칭 듀티비 분할 방식

기존의 제어 방식에서는 하나의 비교기를 사용하여 PWM 신호를 보내 스위칭 하였지만, 제안한 제어 방식은 역률보상 불연속전도모드가 경계전도모드보다 입력전류의 피크값이 높다는 단점을 보완하고 그에 따른 전류 피크값을 저감하기 위하여 스위칭의 듀티비 분할을하였다.

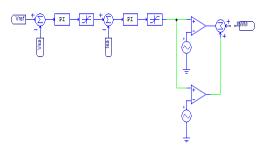

Fig. 19는 제안하는 방식의 블록 다이어그램으로 기존의 방식에서 비교기와 삼각파 제어로직을 추가하였으며, 두 개의 비교기와 삼각파에서 기존의 듀티비를 분할하였다.

각각 비교기가 제어기의 신호와 삼각파의 신호를 받아 서 지연 시간을 주었으며, 이를 통해 스위칭의 듀티비를 분할이 되도록 하였다.

제안한 제어 방식을 주회로에 적용하여 기존 제어 방식과 비교하였으며, PSIM를 통하여 제안한 방식의 듀티비 분할 수와 지연시간에 따른 입력 전류의 피크값을 비교하였다.

Fig. 19. Proposed PFC Control Block Diagram

# 4.2 시뮬레이션 및 비교

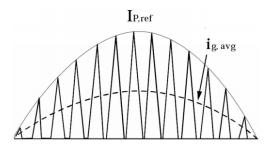

# 4.2.1 스위칭 듀티비 무분할 제어

선정한 주회로에 스위칭의 듀티비를 무분할하였고, 기존의 스위칭 무분할 듀티비 제어를 적용하여 시뮬레이션 하였다.

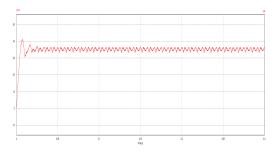

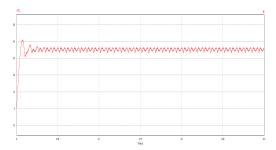

Fig. 20. Switching duty cycle switching current and diode current waveform of splitless control

Fig. 21. Output voltage waveform of switching duty cycle splitless control

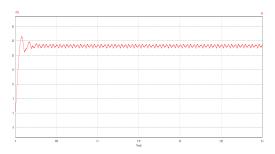

Fig. 20은 스위치 전류와 2차측 다이오드 전류로 각각 7.67A와 8.92A로 측정 되었다. Fig. 21은 회로의 출력 전압으로 31.78V로 2.15V의 리플이 측정 되었다.

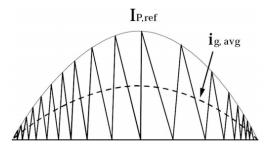

#### 4.2.2 제안하는 스위칭 듀티비 분할 제어

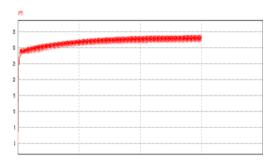

선정한 주회로에 스위치 및 2차측 다이오드 전류의 피 크값을 저감하기 위해 제안한 스위칭 듀티비 분할 제어 를 적용하여 시뮬레이션 하였다.

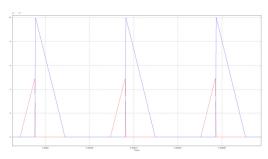

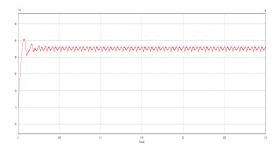

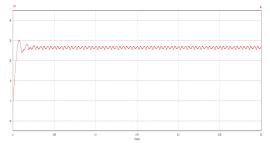

Fig. 22. Switching current and diode current waveform of the proposed switching duty cycle split control

Fig. 23. Output voltage waveform of the proposed switching duty cycle split control

Fig. 22는 스위치 전류와 2차측 다이오드 전류로 각각 6.42A, 6.92A와 5.14A, 5.38A로 측정 되었다. Fig. 23는 회로의 출력 전압으로 31.93V로 2.06V의 리플이 측정 되었다.

# 4.2.3 특성 비교 및 분석

Table 3과 같이 회로를 각각 비교 해보면 스위치 전류가 제안하는 제어 방식은 6.42A, 5.14A로 기존 제어 방식의 7.67A보다 1.25A~2.53A정도 적게 측정 되었으며, 2차측 다이오드 전류는 제안하는 제어 방식이 6.92A, 5.38A로 기존 제어 방식의 8.92A보다 2A정도 적게 측정 되었다.

또, 제안하는 제어 방식으로 스위칭의 듀티비를 분할 하였을 때 출력전압이 기존 방식보다 선정값 33V에 가 깝게 31.93V로 측정 되었으며, 출력 리플이 4% 줄어든 것을 확인할 수가 있었다.

Table 3. Simulation results and circuit comparison table

| control method                    | switching<br>current | diode<br>current | output<br>voltage | ripple |

|-----------------------------------|----------------------|------------------|-------------------|--------|

| non-split control<br>method       | 7.67A                | 8.92A            | 31.78V            | 2.15V  |

| The proposed split control method | 6.42A,<br>5.14A      | 6.92A,<br>5.38A  | 31.93V            | 2.06V  |

# 5. 결론

본 논문에서는 1단 구조 PFC Flyback 컨버터의 전류 리플 저감을 위한 Coupled Inductor LC 공진 Flyback 컨버터를 사용하였으며, 스위치 전류의 피크값을 저감하 기 위해서 스위칭의 듀티비 분할 방식을 제안하였다. 1 단 구조 PFC Flyback 컨버터에서의 제어 방식은 PFC 기능과 스위칭을 하나의 단계로 줄이고, 이를 1차측에서 수행한다. 하지만 회로 특성상 전류의 크기 때문에 플리 커 현상과 소자에 무리를 주어 수명을 단축시키게 된다. 이런 플리커 현상을 줄이고, 소자의 수명을 늘리기 위해 서 듀티비 분할 제어 방식을 선택하였다. 듀티비 분할 제 어 방식은 기존의 PFC 스위칭 제어 블록 구성에 비교기 를 추가하여 듀티비에 지연시간을 주어 스위칭을 조절하 는 방식이다. 이 검증하기 위해서 기존 제어 방식과 제어 하는 듀티비 분할 제어 방식을 PSIM을 통해 시뮬레이션 하여 스위치 전류 및 2차측 다이오드 전류 그리고 출력 전압과 리플을 비교하였으며, 스위칭의 듀티비를 분할하 는 방식이 스위칭 전류 16%와 2차측 다이오드 전류 22%로 저감 되었으며, 출력전압은 선정값이 33V에 더 가까운 31.93V에 출력 리플은 4%로 측정되어 출력 리플 의 저감을 확인하였다.

#### References

- [1] C. T. Kim, "Optimal Hysteresis Control for CCM Driving of a Single-Stage PFC Flyback Converter for LED Lightings", The Transactions of the Korean Institute of Electrical Engineers, pp 586-592, 2016 DOI: https://doi.org/10.5370/KIEE.2016.65.4.586

- [2] T. S. Song, "High Power Factor Flyback-Buck LED driver with Ripple-Free Output Current", 2018 Available From: <a href="http://www.riss.kr/link?id=T14733208">http://www.riss.kr/link?id=T14733208</a>

- [3] J. M. Kim, "Design of BCM based PFC Control IC for LED applications", 2012 Available From:

#### http://www.riss.kr/link?id=T12670065

- [4] Y. S. Jeon, D. L. Jin, J. D. La, Y. S. Kim, "Study of the Elimination of the Electrolytic Capacitors and Reduction of the Ripple Current on the Output Node in the One-Stage PFC Flyback Converter for the LED Lighting", The transactions of The Korean Institute of Electrical Engineers, pp. 1625-1633, 2012. DOI: https://doi.org/10.5370/KIEE.2012.61.11.1625

- [5] K. S. Park, "A High-Efficiency Soft Switching Zero-Voltage-Transition Converter Using Combined Inductor Energy Recovery Circuits", 2001 DOI: https://doi.org/10.1109/ISIE.2001.931553

# 박 대 수(Dae-Su Park)

#### [정회원]

- 2006년 2월 : 건양대학교 디지털 정보제어공학과 (공학사)

- 2013년 2월 : 한국기술교육대학교 대학원 전기공학과 (공학석사)

- 2013년 3월 ~ 현재 : 한국기술교 육대학교 대학원 전기공학과 박사 과정 재학중

〈관심분야〉 전원장치 설계, 신재생에너지

#### 김 태 경(Tae-Kyung Kim)

#### [정회원]

- 2014년 2월 : 한국기술교육대학교 전기공학과 (공학사)

- 2018년 2월 : 한국기술교육대학교 대학원 전기공학과 (공학석사)

- 2018년 3월 ~ 현재 : 한국기술교 육대학교 대학원 전기공학과 박사 과정 재학중

〈관심분야〉 전원장치 설계, 에너지 하베스팅

# 오 성 철(Sung-Chul Oh)

# [정회원]

- 1980년 2월 : 서울대학교 전기공 학과 (공학사)

- 1982년 2월 : 서울대학교 대학원 전기공학과 (공학석사)

- 1989년 5월 : Univ. of Florida

전기공학과 (공학박사)

- 1982년 3월 ~ 1994년 8월 : 한국 전기연구원 선임연구원

- 1994년 9월 ~ 현재 : 한국기술교육대학교 전기전자통신 공학부 교수

〈관심분야〉 전원장치 설계, 전동기제어