# LED 응용을 위한 BCM 방식의 Power Factor Correction Control IC 설계

김지만<sup>1</sup>, 정진우<sup>2</sup>, 송한정<sup>1\*</sup> <sup>1</sup>인제대학교 나노시스템공학과, <sup>2</sup>한국전기연구원, \*인제대학교 나노공학부

# The Design of BCM based Power Factor Correction Control IC for LED Applications

Ji-Man Kim $^1$ , Jin-Woo Jung $^2$  and Han-Jung Song $^{1*}$

<sup>1</sup>Derpartment of Nano Systems Eng., Center for Nano Manufacturing

<sup>2</sup>Korea Electrotechnology Research Institute

\*Derpartment of Nano Eng., Inje University

요 약 본 논문에서는 400V, 120W 급 LED 구동을 위한 1단 전류 경계모드(Boundary Condition Mode) 제어방식의 역률 개선 제어회로를 설계하였다. 제안하는 제어회로는 역률 개선 및 고조파 발생을 감소시키는 기능을 가지고 있으며, 또한 PFC(Power Factor Correction)회로 내에서 상대적으로 많은 면적을 차지하는 기존의 바이폴라 트랜지스터 구조 대신 새로운 CMOS 회로로 설계하였다. 기존대비, 약 30% 정도의 레이아웃 면적을 줄이게 되었고, 상용화 시 칩의 가격 경쟁력이 클 것으로 사료된다.

**Abstract** In this paper, a power factor correction (PFC) control circuit using single stage boundary conduction mode(BCM) for the 400V. 120W LED drive application has been designed. The proposed control circuit is aimed for improvement of the power factor correction and reduction of the total harmonic distortion. In this circuit, a new CMOS multiplier structure is used instead of a conventional BJT(bipolar junction transistor) based multiplier where has a relatively large area. The CMOS multiplier can bring 30 % reduced chip area, competitive die cost in comparison with the conventional BJT multiplier.

Key Words: PFC, LED, Boost DC-DC Convertor, Harmonics, Power Factor

# 1. 서론

최근 들어 에너지 위기와 환경규제 강화, 친환경, 녹색 성장 등이 이슈가 되면서 에너지 절약을 위한 연구가 많 이 요구되는 실정이다. 전력변환 장치를 예로 들자면, 단 순히 전력을 전달하는 역할에서 에너지의 절약을 위하여 에너지의 고효율 및 시스템의 안정성과 신뢰성을 좌우하 는 역할로 확장되어 가고 있다. 전력변환 기술의 전기에 너지 절약에 있어서 효율의 개선과 마찬가지로 꼭 강조 해야 될 성능이 두 가지가 있다. 바로 역률의 개선과 고 조파 발생문제 해결이다.

역률(PF; Power Factor)이란 전원 측으로부터 전달되는 에너지 중 얼마만큼의 에너지가 부하 측에서 유효하게 작용하는 가를 나타내는 요소로서, 역률이 낮으면 무효전력이 상승하기 때문에 전력공급 측면에서 보면 에너지 효율이 상당히 낮게 나타난다[1,2]. 즉 낮은 역률을 갖는 장치는 동일한 전력을 사용할 때 더 큰 입력 전류를 사용하게 되므로, 추가의 발전소가 필요하게 되고 송전 선로와 변전소의 용량도 필요 이상으로 커지게 된다. 전자기기들은 대부분 교류를 직류로 변환하는 커페시터 입

DOI: 10.5762/KAIS.2011.12.6.2707

이 논문은 IDEC 의 반도체 CAD 툴을 사용하여, 2009년도 인제연구장학재단 교수연구년 지원에 의한 연구결과임.

\*교신저자 : 송한정(hjsong@inje.ac.kr)

접수일 11년 04월 11일 수정일 (1차 11년 05월 12일, 2차 11년 05월 13일) 게재확정일 11년 06년 09일

력형 방식의 전파 정류회로를 사용하는데, 이는 스위칭 시 상용전원의 피크치 부분에서 짧은 시간 동안만 정류 기가 도통되어 폭이 좁은 펄스성 전류 파형을 발생하게 된다. 이 펄스성 전류는 다량의 고조파 성분을 포함하여 전력계통에 나쁜 영향을 주는 심각한 문제를 발생시키며, 크게 왜곡된 파형으로 입력 역률을 크게 저하시킨다 [3-5].

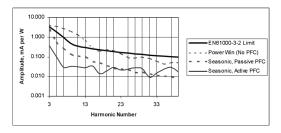

[그림 1] EN 61000-3-2 고조파 규제 [Fig. 1] EN 61000-3-2 Harmonics Regulation

역률 개선 및 고조파 발생 문제 해결은 에너지 절약과 시스템의 안정성을 위해 꼭 필요하다. 이미 유럽을 비롯한 선진 국가에서는 이에 대한 비책으로 그림 1과 같이 EN 61000-3-2 고조파 규제을 통해 고조파 전류를 엄격히 규제하고 있다. 따라서 에너지 손실을 줄이기 위해 역률 개선을 촉진하여 발전 및 송·수전 수요를 감소시키고 전력전송 효율을 개선하기 위하여 이와 관련된 연구가 요구되고 있다. 본 연구에서는 LED 구동을 위해 저 전력 어플리케이션에 필요한 1단 BCM 방식을 사용한 LED 구동용 PFC 제어 IC를 설계하였다.

### 2. 이론적 배경

#### 2.1 역률과 고조파

역률은 피상전력 중에서 유효전력으로 사용되는 비율로 정의된다. 단순히 전압과 전류가 정현파이면 역률은 위상차만 고려한  $\cos\theta$ 로 나타난다. 그러나 부하가 비선 형성인 소자일 때 전류는 정현파가 아니므로, 정현파의 전압과 비 정현파의 전류에 대한 역률은 식 (2)와 같다.

$$PF = \frac{V_{1,\text{r ms}} I_{1,\text{r ms}} \cos \theta}{V_{1,\text{r ms}} I_{rms}}$$

(2)

전고조파의 왜곡율(THD: total harmonics distortion)은 고조파 전압 또는 전류의 실효치와 기본파 전압 또는 전 류의 실효치의 비로 정의되며, 고조파 발생의 정도를 알 수 있다.

$$THD = \sqrt{(\frac{I_{rms}}{I_{1,rms}})^2 - 1} \times 100 \tag{3}$$

왜곡율  $k_d$ 는  $\frac{I_{1,rms}}{I_{rms}}$ 이므로 THD는 식 (3)으로 나타나며

$$THD = \sqrt{\frac{1}{k_d^2} - 1} \times 100 \tag{4}$$

왜곡율  $k_i$ 와 THD사이의 관계에 의하여,

$$k_d = \frac{1}{\sqrt{1 + (\frac{THD}{100})^2}}$$

(5)

$k_d$ 는 식(5)과 같이 정리된다.

따라서 전류와 전압의 기본성분이 동위상이라고 가정했을 때  $k_{ heta} = \cos \theta = 1$ 이 되므로, 이 때의 PF와 THD의 관계를 살펴보면 역률은  $PF = k_d k_{ heta} = k_d$ 로 고조파 성분에 의해서 좌우됨을 알 수 있다[7].

$$PF = \frac{1}{\sqrt{1 + (\frac{THD}{100})^2}} \tag{6}$$

식 (6)에서 알 수 있듯이 THD가 낮을수록 역률이 높 아진다. 따라서 역률을 높이고 고조파를 감소시키면 전력 손실을 줄일 수 있다.

#### 2.2 PFC의 역률 보정

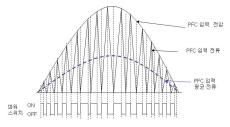

[그림 2] PFC의 입력 전압과 전류 파형 [Fig. 2] Waveform of input voltage and current

그림 2에 PFC의 역률 보정 원리를 설명하기 위한 PFC 의 입력 전압과 전류의 관계를 보여주고 있다. PFC 입력 전압 파형은 AC 브릿지 회로에서 정류된 신호로 제어 회 로 내부의 멀티플라이어에 입력되고, 오차증폭기의 출력 신호와 곱해진다. 파워 스위치가 켜지면 트랜스포머에는 전류가 서서히 증가하기 시작하고, 트랜스포머의 2차측 전류가 멀티플라이어의 출력 전압과 맞닿으면, 파워스위 치가 꺼지게 되어, 0으로 감소하기 시작한다. ZCD는 트 랜스포머의 전류를 멀티플라이어의 출력과 비교되어 파 워 스위치를 켠다[8]. 래치의 리셋에 입력되는 신호는 그 림 2의 파형처럼 인덕터의 전류가 멀티플라이어의 출력 신호와 접촉하는 지점에서 파워 스위치를 꺼서 인덕터 전류를 0으로 떨어지게 하는 기능을 한다. ZCD 신호는 리셋 신호에 의해서 파워 스위치가 꺼지게 되어 인덕터 전류가 0이 될 때, 래치의 셋에 신호를 전달하여 파워 스 위치를 켜게 되며 인덕터의 전류를 증가시키는 기능을 한다. 이와 같이 트랜스포머의 전류를 계속적으로 감지하 여 AC 브릿지 회로의 입력 전압 파형을 따라가게 하여 결과적으로 전압과 전류를 동위상으로 만든다.

# 3. LED 구동용 PFC 제어 IC 설계

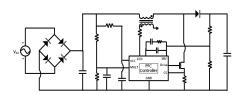

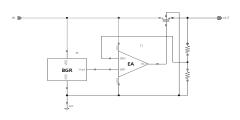

PFC 제어 IC를 구동하기 위하여 그림 3과 같은 단일 스위칭 제어 방식을 사용하였다. PFC 제어 IC는 전류를 거의 정현파에 가깝게 전압위상에 일치하도록 하기위해 입력 브릿지 정류회로와 벌크 커패시터사이에 삽입된다.

[그림 3] 단일 스위칭 방식 PFC 컨버터 구조 [Fig. 3] Structure of single switch PFC converter

PFC 제어 IC를 제외하고 보면 커페시터 입력형 브릿지 다이오드 정류회로에 부스트 회로가 추가된 구조임을 알 수 있다. 인덕터는 트랜스포머를 사용하여 구현하였고, 트랜스포머 2차 측에서 영전류를 검출(ZCD; Zero Current Detector)하도록 설계하였다.

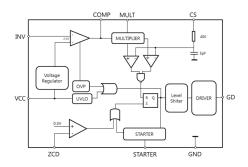

제안하는 제어회로는 1단 BCM 제어방식의 역률 개선 제어회로이며, 그림 4의 구조도와 같이 역률을 개선하는 PFC부분과 저전압 보호회로(UVLO; Under Voltage Lock Out) 및 과전압 보호회로(OVP; Over Voltage Protection)

와 스타터 등의 보호기능을 담당하는 Protection부분으로 나누어진다.

[그림 4] 제안하는 PFC IC의 구조도 [Fig. 4] Structure of proposed PFC IC

#### 3.1 전압 레귤레이터

전압 레귤레이터(voltage regulator)는 전원 전압 VDD를 제공하기 위한 회로로서 그림 5와 같이 기준전압회로 (BGR)와 오차증폭기(EA), 패스트랜지스터, 저항에 의해구성된다[9].

[그림 5] 레귤레이터 회로도 [Fig. 5] Regulator schematic

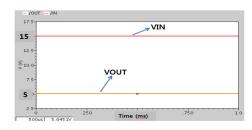

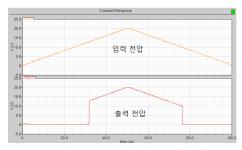

[그림 6] 레귤레이터 입·출력 전압 파형 [Fig. 6] Regulator input and output voltage waveform

외부 PFC구조에서 AC 입력전압은 브릿지 다이오드 정류기를 거쳐 커패시터에 의해 충전되며 제너 다이오드에 의해 그 레벨이 15 V정도로 제한된다. 이 신호를 입력으로 받아 부귀환 구조로 제어하여 온도, 공급전압의 변화에도 안정한 5 V의 전원전압 VDD를 출력하게 된다.

그림 6은 제안하는 PFC 제어 IC 구성 블록인 레귤레이터 의 입,출력 전압에 대한 시뮬레이션을 나타낸 것이다.

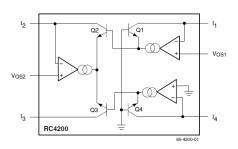

#### 3.2 멀티플라이어

멀티플라이어는 오차증폭기에서 출력되는 오차증폭신 호를 브릿지 다이오드에서 입력되는 Vmult 신호에 반영하여 오차증폭신호의 레벨에 따라 선형적으로 변하는 출력신호를 내보낼 수 있어야 한다. 기존의 상용화된 멀티플라이어의 회로도를 그림 7에 제시하였다.

[그림 7] 상용화된 기존의 멀티플라이어[10] [Fig. 7] Commercial multiplier[10]

기존의 멀티플라이어는 BJT와 OTA 3쌍으로 회로가 구성되어져 있다. 이는 높은 선형성을 가진 멀티플라이어를 구현할 수는 있으나 BJT를 사용하기 때문에 면적이 매우 크고 복잡하다. 따라서 새로운 CMOS로만 이루어진 멀티플라이어의 설계가 필요하다.

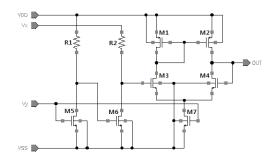

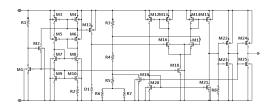

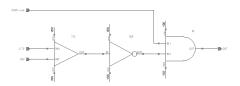

[그림 8] 멀티플라이어 회로도

[Fig. 8] Proposed multiplier schematic

그림 8에 본 논문에서 제안하는 새로운 방식의 CMOS 멀티플라이어를 설계하였다. 설계된 멀티플라이어는 저항 2개와 MOS 7개로 구성되어 매우 구조가 간단하며 기존의 멀티플라이어에 비해 면적의 30 %로 사이즈를 크게 줄일 수 있으며 그에 따라 칩 가격도 낮아진다.

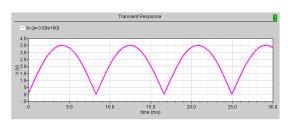

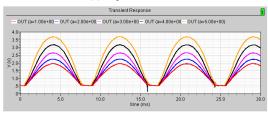

(a) 입력 파형

(b) 출력 파형

(b) Output waveform

[그림 9] 멀티플라이어의 입·출력 파형

[Fig. 9] Input and output waveform of multiplier

PFC IC에서 Vx입력은 Vmult신호가 입력되고 Vy신호는 오차증폭기의 출력신호가 입력되는데, 이 두신호가 곱해져 신호의 제어를 용이하게 한다. 그림 9는 멀티플라이어의 입출력 파형이며, Vmult 신호는 피크전압이 3.5 V가 들어가고 오차증폭기의 출력전압은 1 V에서 5 V까지 5개 전압을 인가하였다. 오차증폭기의 출력전압에 비례하는 멀티플라이어의 출력 전압이 나오고 있다. 멀티플라이어의 출력은 비교기에서 비교가 가능해야 되기 때문에너무 높은 전압이나 보면 비교가 불가능하다. 따라서 멀티플라이어의 출력 범위를 0.5 V이상 4 V이하로 두고 설계하였다.

#### 3.3 보호회로 설계

입력전압이 저전압일 때 제어회로의 오동작이 발생하는 것을 방지하기 위하여 그림 14와 같이 UVLO 보호회로를 설계하였다. 입력전압이 일정 전압이상이 되면 레귤레이터 출력 전압이 목표했던 전압 값에 미치지 못하는데도 내부 제어회로들이 동작을 하여 원하는 동작을 수행하지 않을 수 있다. 이를 보호하기 위해 설계된 UVLO는 히스테리시스 특성을 이용하여 턴-온 되는 전압과 턴-오프 되는 전압이 설정된다.

그림 10의 시뮬레이션 결과처럼 입력전압이 증가할 때 11 V이상이 되면 턴-온 되고, 입력전압이 감소할 때 9 V이하가 되면 턴-오프 된다. 이 구간에서는 레귤레이터 에 전원전압 VDD가 인가되어도 정상적으로 동작할 수

있다.

(a) 저전압 보호회로 회로도 (a) UVLO schematic

(b) 저전압 보호 회로의 시뮬레이션 결과

(b) Simulation waveform of UVLO

[그림 10] 저전압 보호회로

[Fig. 10] Under voltage lockout circuit

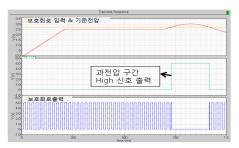

(a) 고전압 보호회로 회로도 (a) OVP schematic

(b) 고전압 보호회로의 시뮬레이션 결과

(b) Simulation waveform of OVP

[그림 11] 고전압 보호회로

[Fig. 11] Over voltage protection circuit

그림 11은 고전압 보호회로 (OVP: over voltage protection)의 회로도 및 시뮬레이션 결과를 나타내고 있다. 출력전압이 목표보다 훨씬 높아지면 소자가 파괴될수 있다. 이를 방지하기 위하여 일정 전압 이상이 될때를 검출하여 이 구간동안은 스위칭 동작을 하지 않도록 제어함으로써 보호할 수 있다. 과전압을 검출하는 것은 간단하게 비교기로 검출할 수 있다.

#### 3.4 PFC 제어 IC의 시뮬레이션

그림 12는 제안하는 PFC 제어 IC의 각 단자별 출력 파형을 나타낸 것이다. ZCD와 CS 단자를 통하여 RS래치의 셋(set)과 리셋(reset)을 만들며, RS래치의 Q값에 의해 파워모스의 동작유무를 결정함으로써 LED 구동용 드라이브 회로의 동작 및 역률을 개선하게 된다. 표 1은 제안하는 PFC 제어 IC의 시뮬레이션 결과를 나타내고 있다.

| CS /<br>MULTO | UT       |    |     |     |     |  |

|---------------|----------|----|-----|-----|-----|--|

| RESET         |          |    |     |     |     |  |

| ZCD           |          | ШШ | WWW | ШШИ | ШИИ |  |

| SET           | <u> </u> |    |     |     |     |  |

[그림 12] PFC 제어 IC 의 각 단자별 출력 파형 [Fig. 12] Output waveform of PFC Control IC

[표 1] 제안하는 PFC 제어 IC 의 시뮬레이션 결과 [Table 1] Simulation results of PFC Control IC

| Parameter                           |     | Unit   |     |     |

|-------------------------------------|-----|--------|-----|-----|

| Farameter                           | min | typ    | max | V   |

| Operating Range                     | 11  |        | 18  | V   |

| Linear Operating<br>Voltage         | -   | 0 to 4 | -   | V   |

| Current Sense<br>Reference Clamp    | 1.3 | 1.8    | 2   | V   |

| Input Threshold Voltage             | -   | 2.3    | -   | V   |

| Dropout Voltage                     | -   | 1.2    | 2   | V   |

| Static OVP Threshold                | 2.5 | 2.7    | 3   | V   |

| Start Timer                         | -   | 150    | -   | us  |

| Power Mosfet<br>Switching Frequency | 50  | 100    | 150 | kHz |

# 4. 결론

본 논문에서는 역률 개선 및 고조파 발생 문제를 해결하기 위하여 1µm High Voltage(20V) CMOS 공정을 이용하여 1단 BCM 제어방식 PFC 제어 IC를 설계하였다. 제안하는 LED구동용 PFC 제어 IC에 적합하도록 BCM 제어방식을 채택하였고, 기존의 멀티플라이어의 면적 및 제조단가를 줄이기 위하여 CMOS로 이루어진 새로운 멀티플라이어를 설계하였으며 설계한 멀티플라이어는 기존의 멀티플라이어에 비해 면적을 30 %로 줄여 칩 가격의 경쟁력이 클 것으로 사료된다. 또한 UVLO 및 OVP 등의보호기능을 내장하여 시스템의 안정성과 신뢰성을 높였다. 케이던스사의 스펙쳐 시뮬레이터를 이용하여 역률보정 기능과 각종 보호회로를 검증하였다.

현재 1 µm High Voltage(20V) CMOS 공정으로 제작 중에 있으며, 향후 칩 제작 후 PFC 제어 IC 특성 시험을 할 예정이다.

#### References

- [1] Roh, Y. S., Moon, Y. J., Gong, J.-C., Yoo, C., "Active Power Factor Correction (PFC) Circuit with Resistor-Free Zero Current Detection", IEEE Transactions on Power Electronics, Vol. PP, pp. 1-1, 2010.

- [2] G. Sauerlander, D. Hente, H. Radermacher, E. Waffenschmidt and J. Jacobs, "Driver Electronics for LEDs," in Industry Applications Conference, 2006. 41th IAS Annual Meeting. Conference Record of the 2006 IEEE, pp. 2621-2626, 2006.

- [3] Y. R. Yang and C. L. Chen, "Analysis of self-excited electronic ballasts using BJTs/MOSFETs as switching devices," Circuits, Devices and Systems, IEE Proceedings -, vol. 145, pp. 95-104, 1998.

- [4] M. Bairanzade, "Electronic Lamp Ballast Design," Application Note ON-SEMI AN1543/D, September, 2000.

- [5] O. Garcia, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "Single Phase Power Factor Correction: A Survey", IEEE Trans. on PE, Vol. 18, No. 3, pp. 749-755, 2003.

- [6] Basso, Christophe P., "Switch Mode Power Supply", McGraw-Hill, 2008.

- [7] X. Ruan, Z. Chen, and W. Chen, "Zero-Voltage -Switching PWM Hybrid Full-Bridge Three-Level Converter", IEEE Trans. on PE, Vol. 20, No. 2, pp. 395-404, 2005.

- [8] ON Semiconductor, "Power Factor Correction Handbook", HBD853/D. Rev.3, Sep-2007

- [9] R. Jacob Baker, "CMOS circuit design, layout, and simulation", Wiley-interscience, 2007.

- [10] Fairchild Semiconductor, "Analog Multiplier RC4200"

#### 김 지 만(Ji-Man Kim)

[정회원]

2010년 2월 : 인제대학교 나노공 학부 (공학사)

2010년 3월 ~ 현재 : 인제대학

교 나노시스템공학과 재학 중

<관심분야> 반도체 회로 설계

# 정 진 우(Jin-Woo Jung)

[정회원]

2009년 2월 : 인제대학교 나노공 학부 (공학사)

2011년 2월 : 인제대학교 나노시 스템공학과 (공학석사)

2011년 3월 ~ 현재 : 한국전기 연구원 위촉연구원

<관심분야> 반도체 회로 설계

# 송 한 정(Han-Jung Song)

[정회원]

1986년 2월 : 한양대학교 전자공 학과 (공학사)

1988년 2월 : 한양대학교 전자공 학과 (공학석사)

2000년 2월 : 한양대학교 전자공 학과 (공학박사)

2004년 3월 ~ 현재 : 인제대학

교 나노공학부 부교수

<관심분야> 반도체 소자 신뢰성 및 회로설계