# 반도체 장비(칠러, 에치 장비)용 SiC-MOSFET 기반 40kW 3상 PWM Active Rectifier 설계에 대한 연구

김시경, 박현상, 이일규, 강대수, 서봉수

공주대학교 천안공과대학

e-mail:skim@kongju.ac.kr

## Design of a SiC-MOSFET-Based 40kW Three-Phase PWM Active Rectifier for Semiconductor Equipment (Chillers and Etch Equipment)

Sikyung Kim, Hyun Sang Park, Ilgyu Lee, Daesoo Kang, Bongsoo Seo

College of Engineering, Kongju National University

### 요약

칠러(Chiller)와 에치(Etch) 장비는 반도체 제조 공정에서 온도 제어 및 식각 공정을 담당하는 핵심적인 장비이며, 이들의 안정적이고 효율적인 운전은 생산 수율을 결정하는 중요한 요소이다. 기존 반도체 장비의 전력 변환 시스템은 주로 다이오드 정류기를 사용해왔다. 그러나 다이오드 정류기는 낮은 역률, 높은 고조파 왜곡(THD), 그리고 전압 강하와 같은 문제점을 야기하며, 이는 전력 시스템의 효율을 저하시키고 전력 품질을 악화시킨다. 또한, 반도체 제조 공정의 에너지 소비가 증가함에 따라, 전력 효율을 극대화하고 전력 품질을 향상시키는 기술의 필요성이 더욱 강조되고 있다.

본 연구에서는 이러한 문제를 해결하기 위한 방안으로 SiC-MOSFET 기반의 3상 PWM Active Rectifier를 제안하였다. SiC(Silicon Carbide)는 기존 실리콘(Si) 소자에 비해 고속 스위칭, 고전압 및 고온 특성이 우수하여 전력 변환 효율을 획기적으로 향상시킬 수 있는 차세대 전력 반도체 소재이다. 이러한 SiC-MOSFET을 적용하면 스위칭 손실을 줄이고, 소자의 소형화 및 경량화를 달성할 수 있다.

### 1. 서론

현대 산업 사회에서 반도체는 디지털 혁명의 핵심이다. 특히, 인공지능(AI), 사물 인터넷(IoT), 빅데이터와 같은 첨단 기술의 발전은 고성능 반도체에 대한 수요를 폭발적으로 증가시키고 있다. 이러한 반도체를 생산하는 과정은 극도로 정밀하고 복잡한 공정을 요구하며, 이 과정에서 사용되는 반도체 장비의 성능은 최종 제품의 품질과 생산성에 직접적인 영향을 미친다. 칠러(Chiller)와 에치(Etch) 장비는 반도체 제조 공정에서 온도 제어 및 식각 공정을 담당하는 핵심적인 장비이며, 이들의 안정적이고 효율적인 운전은 생산 수율을 결정하는 중요한 요소이다. 기존 반도체 장비의 전력 변환 시스템은 주로 다이오드 정류기를 사용해왔다. 그러나 다이오드 정류기는 낮은 역률, 높은 고조파 왜곡(THD), 그리고 전압 강하와 같은 문제점을 야기하며, 이는 전력 시스템의 효율을 저하시키고 전력 품질을 악화시킨다[1].

본 연구의 목표는 반도체 장비에 최적화된 40kW급 SiC-MOSFET 기반 3상 PWM Active Rectifier를 설계하고, 이를 통해 고역률(High Power Factor) 및 저고조파(Low THD) 특성을 구현하는 것이다. 이를 위해 다음과 같은 세부 연구를 수

행하였다. 회로 및 하드웨어 설계: 40kW급 전력 용량을 만족하는 SiC-MOSFET 기반 3상 PWM Active Rectifier의 최적 회로 토폴로지를 선정하고, 스위칭 소자, 인더터, 커�패시터 등 핵심 부품을 설계하는 것이다. 높은 동적 응답 특성 및 안정성을 확보하기 위해 강인 제어(Robust Control) 기법을 적용한 최적의 제어 알고리즘을 개발하는 것이다. 이 알고리즘은 PFC 기능뿐만 아니라 DC 링크 전압 안정화 및 AC 측 전류 제어 기능을 동시에 수행하도록 설계되었다.

### 2. SiC-MOSFET 기반 40kW 3상 PWM Active Rectifier 설계

#### 2.1 SiC-MOSFET PFC(power factor correction) 하드웨어 설계

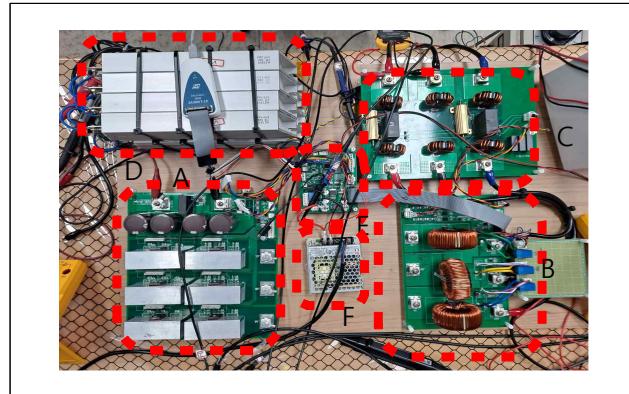

본 연구에서는 고속 스위칭이 가능한 SiC-MOSFET을 활용하여 부하 변동에 따른 역률을 효과적으로 보상하는 3상 정류기를 설계 및 제작하였다. 하드웨어 측면에서는 초기 시스템 보호를 위한 돌입 전류 억제 회로를 구성하였으며, 주 회로부에는 3상 부스트 SiC-MOSFET 구조와 자기 포화 특성이 우수한 페라이트 코어 기반 300 $\mu$ H 부스트 인더터 및 3상 LCL 필터를 제작 적용

하여 3상 AC 전원을 안정적인 400V DC로 승압하였다. SiC-MOSFET의 최적 구동을 위해 STGAP2SICS 갈바닉 절연형 게이트 드라이버를 채택하여 스위칭 손실을 최소화하고 안정도를 높였다. 또한, 정밀한 제어를 위해 입력 및 출력단의 전압과 전류를 감지하는 3상 전류, 전압, DC 링크 전압, 전류 센서들을 구성하였다. 그림 1은 본 연구에서 설계한 SiC-MOSFET 기반 40kW 3상 PWM Active Rectifier 전체 시스템이다.

[그림 1] SiC-MOSFET 기반 40kW 3상 PWM Active Rectifier 전체 시스템,

( A: 3상 SiC-MOSFET, B: 300 $\mu$ H 부스트 인더터, C: 3상 LCL 필터, D: 부하, E: STM32G474RE MCU 제어보드, F: 24V 제어 전원 SMPS )

## 2.2 SiC-MOSFET PFC(power factor correction) 소프트웨어 설계

소프트웨어 구현에 있어서는 STM32G474RE MCU를 기반으로 시스템 상태 점검, 제어 알고리즘, 이상 상태 검출 및 보호, PWM 신호 생성을 위한 네 가지 주요 단계를 체계적으로 구현하였다. 제어 알고리즘의 핵심은 Clarke 및 Park 변환을 이용한 동기 회전 좌표계 제어 방식이며, 이를 통해 PI 제어기가 실측 센서 데이터와 기준값 간의 오차를 계산하여 정밀한 전류 제어를 수행하도록 하였다. 또한, SPWM(Sinusoidal Pulse Width Modulation) 기법을 사용하여 제어된 전류를 SiC-MOSFET의 게이트 구동 신호로 변환하였으며, dq 변환의 기준 위상 동기화를 위해 PLL(Phase-Locked Loop) 알고리즘을 소프트웨어적으로 구현하였다.

## 3. 실험 결과

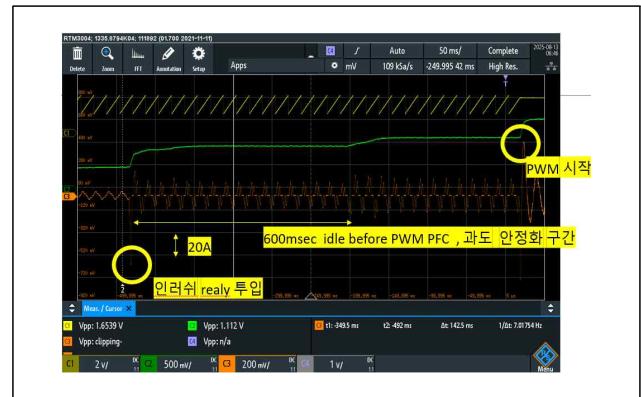

SiC-MOSFET PFC 시스템의 성능을 검증하고자 8kW, 3상 220V 환경에서 실험을 수행하였다. 안정적인 동작을 분석하기 위해 전원 투입 시 돌입 전류 특성을 평가했다. 이를 위해, PWM PFC 동작 전 600ms의 유류 시간(idle time)을 설정하여, 이 기간 동안의 폭넓은 입력 전류를 측정하였고 그림 2는 전원 투입 시 입력 전류 실험 과형이며, 그림 3은 SiC-MOSFET PFC(power factor correction) 실험 결과 과형이며, PFC가 성공적으로 수행됨을 확인할 수 있었다.

[그림 2] 8kw, 3상 220V 조건에서 전원 투입 시 실험 과형

[그림 3] 8kw, 3상 220V 조건에서 SiC-MOSFET PFC(power factor correction) 실험 과형(PWM 상전압 및 전류)

## 4. 기대 효과

본 연구를 통해 설계된 SiC-MOSFET 기반의 3상 PWM Active Rectifier는 다음과 같은 효과가 있을 것으로 기대 된다.

- 에너지 효율 극대화: 고효율 전력 변환을 통해 반도체 장비의 에너지 소비를 절감하며, 이는 생산 비용 감소로 이어진다.

- 전력 품질 향상: 높은 역률과 낮은 고조파 왜곡은 전력 시스템의 안정성을 향상시키고, 다른 장비에 미치는 영향을 최소화하였다.

- 시스템 소형화 및 경량화: SiC-MOSFET의 우수한 특성을 활용하여 전력 변환 시스템의 크기와 무게를 줄일 수 있어 장비의 공간 효율을 높인다.

- 본 연구는 고효율, 고성능 전력 변환 시스템을 필요로 하는 반도체 장비 산업의 기술 경쟁력을 강화하는 데 기여할 것으로 기대된다

## 참고문헌

- [1] Lee, K. W., & Kim, H. J. (2020). Digital current control scheme for boost single-phase PFC converter based on virtual dq transformation. The Transactions of the KIPE, 25(1), 54–60.