# 반도체 검사용 전도성 시트 기반 프로브 블록의 두께 변화에 따른 변위-하중 시뮬레이션 분석

오지연\*, 이예은\*, 박선아\*, 이희준\*

\*미르텍알앤디 주식회사

e-mail : [ohjiveon2242@naver.com](mailto:ohjiveon2242@naver.com), [yaeeun97@naver.com](mailto:yaeeun97@naver.com),

[sunah123456@naver.com](mailto:sunah123456@naver.com), [mirtech77@naver.com](mailto:mirtech77@naver.com)

## Simulation Analysis of Thickness-Dependent Displacement-Load Behavior in Conductive Sheet-Based Probe Blocks for Semiconductor Test Sockets

Ji-yeon Oh\*, Ye-Eun Lee\*, Sun-Ah Park\*, Hee-Joon Lee\*

\*Mirtech R&D Corporation

### 요약

본 연구에서는 반도체 검사용 소켓에 적용 가능한 전도성 시트 기반 프로브 블록을 설계하고, SolidWorks Simulation을 활용하여 정적 구조 해석을 수행하였다. 시뮬레이션은 상부에 0.20 mm에서 0.29 mm 범위의 변위를 인가한 조건에서 하중 반응을 분석하는 방식으로 진행되었다. 해석 결과, 전도층(Cu) 두께 변화는 하중에 유의미한 영향을 주지 않았으나, 절연층인 LCP(Liquid Crystal Polymer) 두께 변화는 구조적 응답에 지배적인 영향을 미쳤다. 특히 LCP 두께가 0.025 mm에서 0.100 mm로 증가할 경우 평균 하중이 약 72% 감소하였으며, 이는 절연층이 두꺼워질수록 구조적 변형을 흡수하고 응력을 분산시키기 때문에 해석된다. 이러한 결과는 전도성 시트 기반 구조가 낮은 하중 조건에서도 안정적인 전기적 접촉을 구현할 수 있음을 보여주며, 차세대 미세 피치 반도체 검사 환경에서 소켓 설계의 새로운 방향성을 제시한다.

### 1. 서론

최근 반도체 패키지는 고성능화, 저전력화, 고집적화를 동시에 충족해야 하는 과제를 요구받고 있다. 이에 따라 검사 공정에서의 정밀성과 신뢰성 확보는 필수적인 요소로 부상하고 있으며, 특히 미세 피치 패키지에서의 검사 안정성은 산업 전반에 직결되는 핵심 문제로 다루어진다[1],[2]. 반도체 검사용 소켓은 DUT(Device Under Test)과 반복적인 전기적 접촉을 형성하는 핵심 부품으로, 접촉의 안정성과 기계적 신뢰성이 보장되지 않을 경우 검사 오류, DUT 손상, 수율 저하로 이어질 수 있다[3]. 현재 널리 사용되는 검사용 소켓은 크게 포고 핀(pogo-pin) 타입과 러버(rubber) 타입으로 나눌 수 있다. 포고 핀 타입은 반복 접촉 내구성이 뛰어나며 고온·고전류 조건에서도 안정적인 특성을 보이는 장점이 있다. 그러나 초미세 피치 환경에서는 충분한 접촉 저항을 확보하기 위해 과도한 하중이 요구되며, 이로 인해 DUT 손상 가능성이 높아진다[4]. 반면 러버 타입은 구조가 단순하고 제작 비용이 낮으며 미세 피치 대응이 용이하다는 장점을 갖지만, 고주파 대역에서 삽입 손실이 커지고 신호 무결성(signal integrity)을 확보하기 어렵다는 한계가 있다[5].

이러한 배경 속에서 전도성 시트 기반 프로브 블록은 낮은 하중 조건에서도 안정적인 전기적 접촉을 구현할 수 있는 대안으로 제안되고 있다. 전도성 시트는 LCP(Liquid Crystal Polymer) 절

연층 위에 Cu와 Au 등의 금속층을 도금한 구조를 가지며, 높은 기계적 강도와 낮은 유전 손실 특성을 동시에 보유한다. 또한 시트 형태의 구조적 특성은 미세 피치 환경에서도 균일한 접촉을 가능하게 해준다[6].

특히 전도성 시트 기반 프로브 블록의 구조적 응답은 소재의 두께 및 물성에 크게 좌우된다. 따라서 SolidWorks Simulation과 같은 유한요소해석(Finite Element Analysis, FEA)을 통해 실제 제작 이전 단계에서 구조적 거동을 분석하는 것은 매우 중요하다. 이는 설계 최적화와 비용 절감뿐 아니라, DUT 보호 및 장기 신뢰성 확보에도 기여할 수 있다. 그러나 전도성 시트 기반 프로브 블록의 유한요소해석을 정밀하게 분석한 논문이 거의 보고되지 않았다[7].

따라서 본 연구에서는 전도성 시트 기반 프로브 블록을 대상으로 변위 조건에 따른 하중 특성을 분석하고, 두께 변화에 따른 하중 감소 경향을 정량적으로 확인하였다. 이를 통해 차세대 반도체 패키지 검사 환경에서 전도성 시트 기반 소켓의 적용 가능성과 기대 효과를 검증하는 것을 목표로 한다.

### 2. 본론

#### 2.1 모델 설계 및 소재 선정

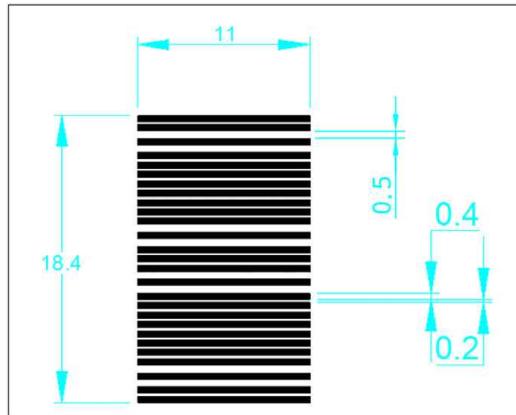

본 연구에서 사용된 프로브 블록은 [그림 1]과 같이 0.6 mm 폐치를 갖도록 설계하였다. 이는 차세대 반도체 패키지의 미세 피치 환경에 적합하도록 고안된 조건으로, 기존 상용 소켓의 한계를 보완하고 차세대 검사 기술 요구에 부합하는 해석을 수행하기 위함이다.

[그림 1] 전도성 시트 기반 미세 피치 설계도

전도성 시트지의 기재로는 LCP(Liquid Crystal Polymer)를 선정하였다. LCP는 약 190 MPa의 탄성계수를 가지며, 우수한 열적 안정성과 낮은 유전 손실 특성을 지녀 고주파 및 고온 환경에서의 신뢰성 있는 성능을 제공한다. 전도층은 전기 전도성이 우수한 구리(Cu)를 적용하였다. 한편, 전도성 시트지를 제외한 나머지 구조는 [그림 2]와 같이 단일 블록 배열 형태로 구성하였다. 시뮬레이션에 사용된 각 재료의 물성치는 [표 1]에 요약하였다.

[표 1] 각 재료의 물성치

| 재료                       | 탄성계수<br>(E, N/mm <sup>2</sup> ) | 포아송비 ν | 밀도<br>(ρ, kg/m <sup>3</sup> ) |

|--------------------------|---------------------------------|--------|-------------------------------|

| Cu                       | 110,000                         | 0.37   | 8,900                         |

| Si                       | 112,400                         | 0.28   | 2,330                         |

| LCP<br>(초저밀도 PE)         | 172                             | 0.3    | 905                           |

| SUS<br>(Stainless steel) | 200,000                         | 0.28   | 7,800                         |

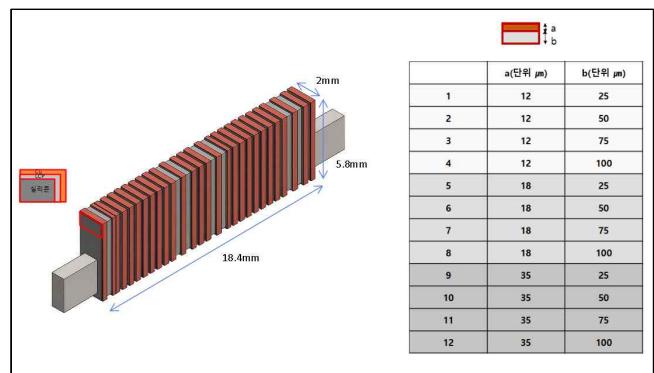

## 2.2 시뮬레이션 조건

본 연구의 시뮬레이션은 SolidWorks Simulation을 활용하여 수행하였다. 경계 조건은 하단을 고정(Fixed support), 측면을 슬라이드(Slide) 조건으로 설정하였으며, 상단에는 압축 하중을 인가하였다. [그림 2]는 블록 모델링과 함께, Cu 및 LCP 두께를 변수로 설정한 조건을 나타낸다.

[그림 2] 블록 모델링 및 두께 조건 표

하중 조건은 상부에서 0.20 mm에서 0.29 mm까지의 변위를 가하는 방식으로 설정하였다. 출력 결과로는 하중(Force, N)과 응력 분포(Stress distribution, MPa)를 도출하였으며, 이를 분석에 활용하였다.

## 3. 시뮬레이션 결과 및 고찰

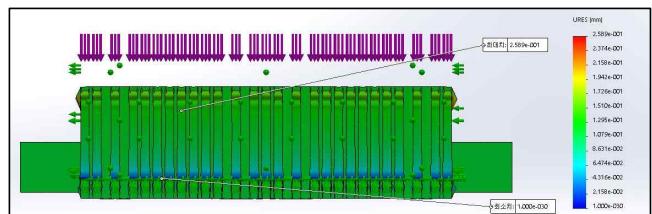

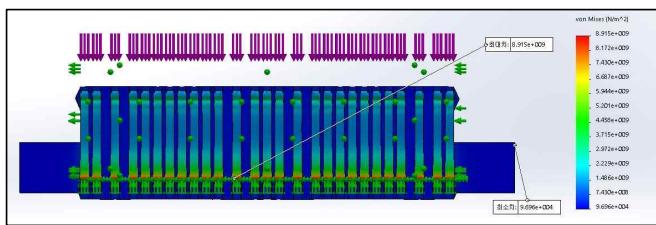

시뮬레이션 해석 결과, 전도성 시트 기반 프로브 블록의 구조적 거동은 두께 변화에 따라 뚜렷한 차이를 보였으나, 전체적으로 유사한 경향을 나타냈다. 모든 조건에서 전반적으로 유사한 거동 양상이 확인되었기 때문에 전체 결과 중 대표적인 이미지만을 선별하여 제시하였다. [그림 3]은 조건6(Cu 두께 0.018mm, LCP 두께 0.05mm)에서의 변위 분포 해석 결과이며, [그림 4]는 동일 조건에서의 응력 분포 해석 결과를 보여준다.

변위 해석에서는 상부 하중 인가 시 블록 전체가 압축되면서 특정 국부 영역에 변위가 집중되는 양상이 관찰되었으며, 이는 접촉 정밀도의 저하로 이어질 수 있는 잠재적 요인으로 평가된다. 또한, 응력 해석에서는 접촉부 및 모서리에서 뚜렷한 응력 집중(stress concentration)이 나타났으며, 이는 반복 접촉 과정에서 DUT 손상 및 소켓 내구성 저하로 직결될 가능성을 시사한다. 이러한 결과는 과도한 사용 조건에서 누적 응력이 발생하여 문제를 유발할 수 있는 경우로 해석되며, 일반적인 사용 환경에서는 큰 무리 없이 적용이 가능하다고 판단된다.

[그림 3] SolidWorks 변위해석

[그림 4] SolidWorks 응력해석

그림 2에서 제시한 모든 조건에 대한 시뮬레이션 결과를 [표 2]에 정리하였다. Cu 두께가 0.012 mm, 0.018 mm, 0.035 mm로 변화할 때 평균 하중은 각각 약 850 N, 845 N, 865 N으로, 유의미한 차이가 관찰되지 않았다. 반면, LCP 두께가 0.025 mm에서 0.100 mm로 증가할 경우 평균 하중은 약 72% 감소하였다. 이는 절연층 두께가 증가함에 따라 구조적 변형을 더 많이 흡수하고 응력을 효과적으로 분산시킨 결과로 해석된다.

[표 2] 시뮬레이션 결과 정리 표

|    | Cu 두께 (mm) | LCP 두께 (mm) | Force Min (N) | Force Max (N) | Force Avg (N) |

|----|------------|-------------|---------------|---------------|---------------|

| 1  | 0.012      | 0.025       | 700           | 1000          | 850           |

| 2  | 0.012      | 0.050       | 360           | 530           | 445           |

| 3  | 0.012      | 0.075       | 250           | 360           | 305           |

| 4  | 0.012      | 0.100       | 190           | 270           | 230           |

| 5  | 0.018      | 0.025       | 690           | 1000          | 845           |

| 6  | 0.018      | 0.050       | 370           | 540           | 455           |

| 7  | 0.018      | 0.075       | 250           | 360           | 305           |

| 8  | 0.018      | 0.100       | 190           | 270           | 230           |

| 9  | 0.035      | 0.025       | 700           | 1030          | 865           |

| 10 | 0.035      | 0.050       | 370           | 540           | 455           |

| 11 | 0.035      | 0.075       | 250           | 370           | 310           |

| 12 | 0.035      | 0.100       | 190           | 280           | 235           |

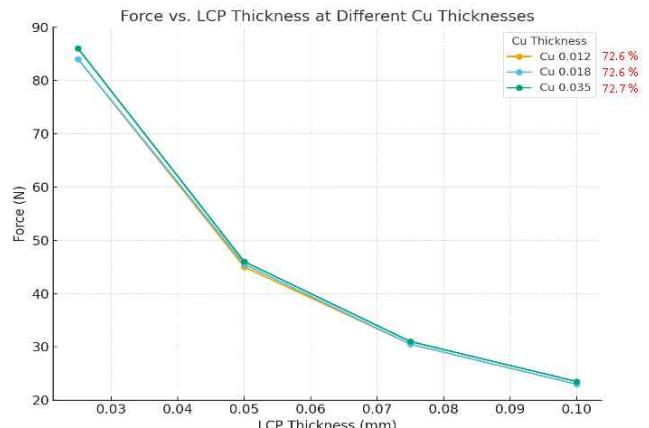

이러한 경향을 보다 명확히 하기 위해, LCP 두께 증가에 따른 평균 하중 감소율을 Cu 두께별로 정리한 결과를 [표 3]에 제시하였다. 모든 조건에서 평균 약 72%의 감소율을 보였으며, 이는 Cu 두께와 무관하게 LCP 두께가 구조적 응답을 지배하는 핵심 인자임을 시사한다. [그림 5] 역시 동일한 결과를 시작적으로 보여주고 있으며, LCP 두께 증가에 따라 평균 하중이 선형적으로 감소하는 경향이 뚜렷하게 나타났다.

따라서, [표 2]의 전체 결과와 이를 해석·정리한 [표 3] 및 [그림 5]를 종합하면, LCP 두께는 구조적 거동을 결정짓는 주요 설계 변수임을 확인할 수 있으며, 이를 최적화함으로써 DUT 보호와 접촉 신뢰성을 동시에 확보할 수 있음을 알 수 있다.

[그림 5] Cu 두께별 LCP 두께 변화에 따른 평균 하중 그래프

[표 3] LCP 두께 증가에 따른 평균 하중 감소율

| Cu_thickness (mm) | Force Avg_at_LCP0.025(N) | Force Avg_at_LCP0.1(N) | Reduction (%) |

|-------------------|--------------------------|------------------------|---------------|

| 0.012             | 850                      | 230                    | 72.94         |

| 0.018             | 845                      | 230                    | 72.75         |

| 0.035             | 865                      | 235                    | 72.83         |

#### 4. 결론

본 연구에서는 전도성 시트 기반 프로브 블록의 기계적 응답을 SolidWorks Simulation을 통해 해석하고, 변위 조건(0.20~0.29 mm)에서 도금층과 절연층의 두께 변화가 하중-응력 거동에 미치는 영향을 분석하였으며, 주요 결론은 다음과 같다.

첫째, 절연층인 LCP 두께가 증가할수록 평균 하중은 급격히 감소하였으며, 0.025 mm에서 0.100 mm로 증가할 경우 약 72%의 감소율을 보였다. 이는 절연층이 구조적 변형을 흡수하고 응력을 분산시켜, 접촉 과정에서 DUT(Device Under Test)를 보호하는 역할을 수행함을 의미한다. 반면, 전도층인 Cu 두께 변화는 평균 하중에 유의미한 영향을 주지 않았으며, 이는 Cu가 구조적 강성보다는 전기적 전도성 확보에 기여함을 보여준다.

둘째, 변위 및 응력 분포 해석에서 접촉부와 모서리 영역에서의 응력 집중(stress concentration)이 확인되었다. 이러한 결과는 과도한 사용 조건에서 누적 응력이 발생하여 DUT 손상 및 소켓 내구성 저하를 유발할 수 있는 경우로 해석되며, 일반적인 사용 환경에서는 큰 무리 없이 적용이 가능하다고 판단된다.

이상의 결과를 종합하면, 전도성 시트 기반 프로브 블록은 낮은 하중 조건에서도 안정적인 전기적 접촉을 구현할 수 있으며, 기존 포고 핀이나 러버 타입 소켓의 한계를 보완할 수 있는 대안으로 평가된다. 특히 초미세 피치 반도체 패키지 검사 환경에서

DUT 보호와 검사 신뢰성을 동시에 확보할 수 있다는 점에서 산업적 의의가 크다.

향후 연구에서는 실제 시제품 제작을 진행하고, 이를 대상으로 기계적 및 전기적 특성 평가를 수행하고자 한다. 이를 통해 전도성 시트 기반 소켓은 차세대 반도체 검사 공정 적용을 위한 상용화 수준의 설계 지침으로 발전할 수 있을 것으로 기대된다.

**감사의 글**

본 연구는 2024년도 과학기술정보통신부 2024-DD-RD-0105-01의 지원에 의하여 이루어진 연구로서, 관계 부처에 감사드립니다.

**참고문헌**

- [1] 김진수, 박성호, “반도체 패키징 기술 동향과 신뢰성 평가,” 전자공학회지, vol. 60, no. 3, pp. 23–31, 2023.

- [2] 이종현, “고집적 반도체 검사 공정의 기술적 과제,” 한국반도체디스플레이기술학회 논문집, vol. 12, no. 2, pp. 45–52, 2022.

- [3] Zahra Ehtiatkar, Salman Basiri, Nowshad Amin, “Mechanical design and analysis of innovative integrated circuit test socket,” IEEE Conference on Semiconductor Electronics, pp. 356–360, 2010.

- [4] K. M. Lee, S. Ahn, E. Park, M. Kim, “Low-loss pogo pin probe card with coupling isolation structure up to 50 GHz,” Sensors, vol. 23, no. 11, 2023.

- [5] Lam H. K., Koay C. Y., Amin N., “Semiconductor final test fixture design with microstructure alloy contacts using finite element analysis,” Microelectronics Reliability, vol. 50, pp. 920–927, 2010.

- [6] 김태경, 박선영, “전도성 고분자 시트의 전기적 특성과 응용 가능성,” 한국전기전자재료학회 논문집, vol. 36, no. 4, pp. 281–289, 2023.

- [7] T. K. Kim, “Fabrication and characterization of three-dimensional MEMS spring structure coaxial socket for semiconductor chip package testing,” Micromachines, vol. 14, no. 2, 2023.